Purpose

Device Control Blocks (DCBs) are static tables used to describe the board topology and connections external to the GPU chip.

Each board built has specific additions to the capabilities through external devices, as well as limitations where output lines are not linked to device connectors. DCBs define the devices connected, specific information needed to configure those devices, and the external electrical connections such as HDMI and Display Port.

DCBs do not try to explain the capabilities of the chip itself. That information is implicit in the VBIOS, firmware and drivers, which are built differently for each chip. Both the firmware and the drivers know the inherent capability of each chip, and use runtime choices to determine chip dependent code paths.

-

DCB 1.x is used with Core3 VBIOS (NV5, NV10, NV11, NV15, NV20).

-

DCB 2.x (2.0-2.4) is used with Core4 and Core4r2 VBIOS (NV17, NV25, NV28, NV3x).

-

DCB 3.0 is used with Core5 VBIOS (NV4x, G7x).

-

DCB 4.0 is used with Core6, Core7, and Core8 VBIOS (G80+).

Device Control Block Structure

The 4.0 DCB Data Structure consists of the following parts:

-

Header - The version number (0x40 for Version 4.0), the header size, the size of each DCB Entry (currently 8 bytes), the number of valid DCB Entries, pointers to different tables, and the DCB signature. If any of the pointers here are NULL, then those tables are considered to be absent or invalid.

-

Device entries list - One for each display connector (two for DVI-I connectors). Each device entry is subdivided into two main parts: Display Path Information and Device Specific Information.

Device Control Block Header

| Name | Bit width | Optional/Mandatory | Values and Meaning |

|---|---|---|---|

Version |

8 |

O |

Version # of the DCB Header and Entries. DCB 4.0 will start with a value of 0x40 here. A version number of zero directs the driver to use an internal DCB table. |

Header Size |

8 |

M |

Size of the DCB Header in Bytes. For v4.0 this will be 27 bytes. |

Entry Count |

8 |

M |

Number of DCB Device Entries immediately following this table. |

Entry Size |

8 |

M |

Size of Each Entry in bytes. With the start of DCB 4.0, this field should be 8. |

Communications Control Block Pointer |

16 |

M |

Pointer to the Communications Control Block. In v3.0 this was the I2C Control Block Pointer. |

DCB Signature |

32 |

M |

DCB signature = 0x4EDCBDCB. This is used to tell a valid DCB from an invalid one. |

GPIO Assignment Table Pointer |

16 |

M |

Pointer to the GPIO Assignment Table. |

Input Devices Table Pointer |

16 |

O |

Pointer to the Input Devices Table. |

Personal Cinema Table Pointer |

16 |

O |

Pointer to the Personal Cinema Table. |

Spread Spectrum Table Pointer |

16 |

O |

Pointer to the Spread Spectrum Table. |

I2C Devices Table Pointer |

16 |

O |

Pointer to the I2C Devices Table. |

Connector Table Pointer |

16 |

M |

Pointer to the Connector Table. |

Flags |

8 |

M |

See DCB Flags below |

HDTV Translation Table Pointer |

16 |

O |

Pointer to the HDTV Translation Table. This structure is optional. If the structure is not needed, then this pointer can be set to 0. |

Switched Outputs Table Pointer |

16 |

O |

Pointer to the Switched Outputs Table. This structure is optional. |

An "optional" table pointer or field may be set to zero to indicate that no table is present. If the structure is not needed, then this pointer can be set to 0.

|

Note

|

Throughout this document, a "pointer" means a byte offset relative to the start of the VBIOS image. |

DCB Flags

Each bit flag has a different meaning. All undefined bits are reserved and must be set to 0.

-

Bit 0 - Boot Display Count:

-

0 - Only 1 boot display is allowed.

-

1 - 2 boot displays are allowed.

-

These next 2 bits are all used for VIP connections.

-

Bits 5:4 - VIP location. Possible values are:

-

00b - No VIP.

-

01b - VIP is on Pin Set A.

-

10b - VIP is on Pin Set B.

-

11b - Reserved

-

These next 2 bits are used for Distributed Rendering (DR) configuration.

-

Bit 6 - All capable DR ports: Pin Set A:

-

1 - Pin Set A is routed to a SLI Finger.

-

0 - Pin Set A is not attached.

-

-

Bit 7 - All capable DR Ports: Pin Set B:

-

1 - Pin Set B is routed to a SLI Finger.

-

0 - Pin Set B is not attached.

-

|

Note

|

A PIOR port cannot be used both as a Distributed Rendering connection and as an Output Display at the same time. |

DCB Header Version 4.0 Sizes

The v4.0 DCB header has added fields over time.

| DATE | New Size | Last Inclusive Field |

|---|---|---|

Start |

23 Bytes |

Flags |

08-02-06 |

25 Bytes |

DCB 3.0, HDTV Translation Table Pointer |

11-07-06 |

27 Bytes |

Switched Outputs Table Pointer |

DCB Device Entries

A DCB device entry is 64 bits wide, two double words. The first 32 bits, Display Path Information, contain the main routing information. Their format is common to all devices. The second 32 bits, Device Specific Information, are interpreted based on the Type field from the Display Path Information.

There is one device entry for each output display path. The number of DCB entries is listed in the DCB Header.

|

Note

|

For DVI-I connectors there are two entries: one for the CRT and one for the LCD. The two device entries share the same I2C port. |

Device Entries are listed in order of boot priority. The VBIOS code will iterate through the DCB entries and if a device is found, then that device will be configured. If not, the VBIOS moves to the next index in the DCB. If no device is found, the first CRT on the list should be chosen.

GPUs earlier than G80 have a "mirror mode" feature that enables up to two display devices to be enabled by the VBIOS, and controlled through the same VGA registers. G80 and later display hardware only supports one display in VGA mode, and the VBIOS will only enable one display device.

When Device Entries are listed, it is not allowed to have two entries for the same output device.

Display Path Information

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Rsvd |

VD |

Output Devices |

BBDR |

BDR |

Loc |

Bus |

Connector |

Head |

EDID Port |

Type |

|||||||||||||||||||||

| Name | Bit width | Values and Meaning |

|---|---|---|

Type |

4 |

Display type. |

EDID |

4 |

EDID Port. |

Head |

4 |

Head bitmask. |

Con |

4 |

Connector table entry index. |

Bus |

4 |

Logical bus, used for mutual exclusion. |

Loc |

2 |

Location of the final stage devices, on-chip or off-chip. |

BDR |

1 |

Disables this as a boot display if set. |

BBDR |

1 |

If set, disables the ability to boot if not display is detected. |

VD |

1 |

Indicates this is a virtual device. |

Rsvd |

3 |

Reserved, set to 0. |

This field defines the Type of the display used on this display path. Currently defined values are:

-

0 = CRT

-

1 = TV

-

2 = TMDS

-

3 = LVDS

-

4 = Reserved

-

5 = SDI

-

6 = DisplayPort

-

E = EOL (End of Line) - This signals the SW to stop parsing any more entries.

-

F = Skip Entry - This allows quick removal of entries from DCB.

Each number refers to an entry in the Communications Control Block Structure that represents the port to use in order to query the EDID. This number cannot be equal to or greater than the Communication Control Block Header’s Entry Count value, except if the EDID is not retrieved via DDC (over I2C or DPAux).

For DFPs, if the EDID source is set to straps or SBIOS, then this field must be set to 0xF to indicate that we are not using a Communications Control Block port for this device to get the EDID.

Each bit defines the ability of that head with this device.

-

Bit 0 = Head 0

-

Bit 1 = Head 1

-

Bit 2 = Head 2

-

Bit 3 = Head 3

GPUs before GK107 only support two heads. For those devices, bits 2 and 3 should always be zero.

This field signifies a specific entry in the Connector Table. More than one DCB device can have the same Connector Index. This number cannot be equal to or greater than the Connector Table Header’s Entry Count value.

|

Note

|

If two DCB entries have the same Connector Index, that still allows them to be displayed at the same time. To prevent combinations based on the connector, use the Bus field. |

This field only allows for logical mutual exclusion of devices so that they cannot display simultaneously. The driver uses this field to disallow the use of a combination of two devices if they share the same bus number.

This field shows the location of the last output device before the data is sent off from our board to the display.

Currently defined values are:

-

0 = On Chip (internal) TV encoder, internal TMDS encoder

-

1 = On Board (external) DAC, external TMDS encoder

-

2 = Reserved.

-

0 = This device is allowed to boot if detected.

-

1 = This device is not allowed to boot, even if detected.

-

0 = This device is allowed to boot if no devices are detected.

-

1 = This device is not allowed to boot if no devices are detected.

Each bit defines the use of this connector with a DAC for internal CRTs and TVs, an SOR for internal DFPs, and a PIOR for external devices like TMDS, SDI or TV Encoders.

Currently defined values are:

-

Bit 0 = DAC 0, SOR 0, or PIOR 0

-

Bit 1 = DAC 1, SOR 1, or PIOR 1

-

Bit 2 = DAC 2, SOR 2, or PIOR 2

-

Bit 3 = DAC 3, SOR 3, or PIOR 3

-

0 = This is a physical device.

-

1 = This is a virtual device.

Virtual devices are used only for remote desktop rendering. When set to 1, EDID Port should be set to 0xF (unused) and the Connector Index should reference an entry with Type="Skip Entry".

The BUS field may reflect only a logical limitation of the buses. It can describe an actual physical limitation, or it may be solely a way to remove the combination between two DCB entries.

Device Specific Information

Each device type has a different specific information associated with it. However, TMDS, LVDS, SDI, and DisplayPort share the same DFP Specific Information.

CRT Specific Information

| 31..0 |

|---|

Reserved (Set to 0) |

DFP Specific Information

DFP Specific Information is used to decribe TMDS, LVDS, SDI and DisplayPort Types of devices.

| 31..28 | 27..24 | 23..21 | 20 | 19..18 | 17 | 16 | 15..8 | 7..6 | 5..4 | 3..2 | 1..0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

Rsvd |

MxLM |

MLR |

E |

Rsvd |

HDMI |

Rsvd |

Ext Enc |

Rsvd |

SL/DPL |

Ctrl |

EDID |

| Name | Bit width | Values and Meaning |

|---|---|---|

EDID |

2 |

EDID source. |

Ctrl |

2 |

Power and Backlight Control. |

SL/DPL |

2 |

Sub-link/DisplayPort Link. |

Rsvd |

2 |

Reserved, set to 0. |

Ext Enc |

8 |

External Link Type. |

Rsvd |

1 |

Reserved. |

HDMI |

1 |

HDMI Enable. |

Rsvd |

2 |

Reserved, set to 0. |

E |

1 |

External Communications Port. |

MxLR |

3 |

Maximum Link Rate. |

MxLM |

4 |

Maximum Lane Mask. |

Rsvd |

4 |

Reserved, set to 0. |

This field states where to get the EDIDs for the panels. Current values are:

-

0 = EDID is read via DDC.

-

1 = EDID is determined via Panel Straps and VBIOS tables.

-

2 = EDID is obtained using the _DDC ACPI interface or VBIOS 5F80/02 SBIOS INT15 calls.

-

3 = Reserved.

There is a secondary fallback policy that is used for all mobile LVDS panels. It follows this convention:

| DCB EDID Source | Panel Strap | Panel Index | EDID Retrieval |

|---|---|---|---|

DDC |

== 0xF |

Don’t Care. |

Use DDC. |

!= 0xF |

Don’t Care. |

Use Straps and VBIOS Tables. |

|

Straps and VBIOS Tables |

!= 0xF |

Don’t Care. |

Use Straps and VBIOS Tables. |

== 0xF |

!= 0xF |

Use Straps and VBIOS Tables. |

|

== 0xF |

No Panel. |

||

SBIOS |

Don’t Care. |

Don’t Care. |

Use SBIOS _DDC ACPI method or SBIOS/VBIOS Call. |

If the board designer chooses to use DDC based EDIDs always, the VBIOS can override the Panel Strap to always indicate 0xF via SW Strap Overrides or through the DevInit scripts.

This field describes the control method for the power and backlight of the panel. Currently defined values are:

-

0 = External. This is used to define panels where we don’t have direct control over the power or backlight. For example, this value is used for most TMDS panels.

-

1 = Scripts. Used for most LVDS panels.

-

2 = VBIOS callbacks to the SBIOS.

This field specifies a board-supported sub-link mask for TMDS, LVDS, and SDI. For Display Port, this field specifies the link mask supported on the board.

For TMDS, LVDS, and SDI, this field lists which sub-links in each SOR are routed to the connector on the board.

Possible sub-link values are:

-

Bit 0: Sub-link A

-

Bit 1: Sub-link B

If both sub-links are routed to the connector, specifying a dual-link connector, then bits 0 and 1 will both be set.

|

Note

|

Dual-link hook-up does not necessarily mean that both links should be used during programming. According to the DVI 1.0 specification, the crossover frequency of 165 MHZ should be the deciding factor for when dual-link vs. single-link connections should be used for TMDS use. This field merely indicates whether the connector has two links connected to it. It does not specify the actual use of either single-link or dual-link connections. |

LVDS uses single-link or dual-link connections based on the individual panel model’s requirements. For example, SXGA panels may be run with single-link or dual-link LVDS connections.

For DisplayPort, this field describes which links in each SOR are routed to the connector on the board. Possible link values are:

-

Bit 0: DP-A (Display Port Resource A)

-

Bit 1: DP-B (Display Port Resource B)

|

Note

|

Unlike TMDS, LVDS, and SDI, if both links are routed to the connector, this does not indicate the presence of a dual-link connector. It simply means that both Display Port (DP) resources A and B may be used with this SOR. That is: DP-A or DP-B may be associated with an output device (OD) to output via DisplayPort, but not both simultaneously. |

Set to 0.

This field describes the exact external link used on the board. If this Location field in the Display Path of this DCB entry is set to ON CHIP, then these bits should be set to 0.

Currently defined values:

This bit is placed here to allow the use of HDMI on this particular DFP output display.

Currently defined values are:

-

0 = Disable HDMI on this DFP

-

1 = Enable HDMI on this DFP

If this device uses external I2C or DPAux communication, then this field allows us to know which port is to be used. If the device is internal to the chip, set this bit to 0 by default.

Currently defined values are:

-

0 = Primary Communications Port

-

1 = Secondary Communications Port

The Communications Control Block Header holds the primary and secondary port indices. Each index maps to an entry in the Communications control Block table, which specifies the physical port and type to use to communicate with this device.

This field describes the maximum link rate allowed for the links within the Display Port connection. This field is only applicable to DisplayPort device types.

Possible values are:

0 |

1.62 Gbps |

1 |

2.7 Gbps |

2 |

5.4 Gbps |

This field describes the maximum lanes that are populated on the board. This field is only applicable to DisplayPort device types.

Possible values are:

0x1 |

1 Lane |

0x3 |

2 Lanes |

0xF |

4 Lanes |

| Value | Name | I2C Addr |

|---|---|---|

0 |

Undefined (allows backward compatibility) - Assumes Single-Link. |

|

1 |

Silicon Image 164 - Single-Link TMDS. |

0x70 |

2 |

Silicon Image 178 - Single-Link TMDS. |

0x70 |

3 |

Dual Silicon Image 178 - Dual-Link TMDS. |

0x70 (primary), 0x72 (secondary) |

4 |

Chrontel 7009 - Single-Link TMDS. |

0xEA |

5 |

Chrontel 7019 - Dual-Link LVDS. |

0xEA |

6 |

National Semiconductor DS90C387 - Dual Link LVDS. |

|

7 |

Silicon Image 164 - Single-Link TMDS (Alternate Address). |

0x74 |

8 |

Chrontel 7301 - Single-Link TMDS. |

|

9 |

Silicon Image 1162 - Single Link TMDS (Alternate Address). |

0x72 |

A |

Reserved |

Reserved |

B |

Analogix ANX9801 - 4-Lane DisplayPort. |

0x70 (transmitter), 0x72 (receiver) |

C |

Parade Tech DP501 - 4-Lane DisplayPort. |

|

D |

Analogix ANX9805 - HDMI and DisplayPort. |

0x70, 0x72, 0x7A, 0x74 |

E |

Analogix ANX9805 - HDMI and DisplayPort (Alternate Address). |

0x78, 0x76, 0x7E, 0x7C |

TV Specific Information

| 31..24 | 23..20 | 19..16 | 15..8 | 7..4 | 3..0 |

|---|---|---|---|---|---|

Rsvd |

HDTV |

CC |

E |

DACS+ |

Encoder |

| Name | Bit width | Values and Meaning |

|---|---|---|

SDTV |

3 |

SDTV Format. |

Rsvd |

1 |

Reserved, set to 0. |

DACs |

4 |

DAC description, lower four bits. |

Encoder |

8 |

Encoder identifier. |

TVDACs+ |

4 |

DAC description, upper four bits. |

E |

1 |

External Communication Port. |

CC |

2 |

Connector Count. |

HDTV |

4 |

HDTV Format. |

Rsvd |

5 |

Reserved, set to 0. |

This field determines the default SDTV Format.

Currently defined values are:

-

0x0 = NTSC_M (US)

-

0x1 = NTSC_J (Japan)

-

0x2 = PAL_M (NTSC Timing w/PAL Encoding - Brazilian Format)

-

0x3 = PAL_BDGHI (US)

-

0x4 = PAL_N (Paraguay and Uruguay Format)

-

0x5 = PAL_NC (Argentina Format)

-

0x6 = Reserved

-

0x7 = Reserved

These bits define the availability of encoder outputs that the board supports to the TV connectors.

| Value | Meaning |

|---|---|

0x00 |

Reserved. |

0x01 |

Invalid. |

0x02 |

CVBS on Green. |

0x03 |

CVBS on Green and S-Video on Red (chroma) and Green (luma). |

0x04 |

CVBS on Blue. |

0x05 |

Invalid. |

0x06 |

Invalid. |

0x07 |

CVBS on Blue, S-Video on Red (chroma) and Green (luma). |

0x08 |

Standard HDTV. |

0x09 |

HDTV Twist 1. |

0x0A |

SCART. |

0x0B |

Twist 2. |

0x0C |

SCART + HDTV. |

0x0D |

Standard HDTV without SDTV. |

0x0E |

SCART Twist 1. |

0x0F |

SCART + HDTV. |

0x11 |

Composite + HDTV outputs. |

0x12 |

HDTV + Scart Twist 1. |

0x13 |

S-Video on Red (chroma) and Green (luma). |

This field describes the exact encoder used on the board.

-

Brooktree/Conexant

-

0x00 = Brooktree 868

-

0x01 = Brooktree 869

-

0x02 = Conexant 870

-

0x03 = Conexant 871

-

0x04 = Conexant 872

-

0x05 = Conexant 873

-

0x06 = Conexant 874

-

0x07 = Conexant 875

-

-

Chrontel

-

0x40 = Chrontel 7003

-

0x41 = Chrontel 7004

-

0x42 = Chrontel 7005

-

0x43 = Chrontel 7006

-

0x44 = Chrontel 7007

-

0x45 = Chrontel 7008

-

0x46 = Chrontel 7009

-

0x47 = Chrontel 7010

-

0x48 = Chrontel 7011

-

0x49 = Chrontel 7012

-

0x4A = Chrontel 7019

-

0x4B = Chrontel 7021

-

-

Philips

-

0x80 = Philips 7102

-

0x81 = Philips 7103

-

0x82 = Philips 7104

-

0x83 = Philips 7105

-

0x84 = Philips 7108

-

0x85 = Philips 7108A

-

0x86 = Philips 7108B

-

0x87 = Philips 7109

-

0x88 = Philips 7109A

-

-

NVIDIA

-

0xC0 = NVIDIA internal encoder

-

This field shows bits 4-7 of the TVDACs value.

If this device uses external I2C communication, then this field allows us to know which device will be used. If the device is internal to the chip, set this bit to 0 as default.

Currently defined values are:

-

0 = Primary Communications Port

-

1 = Secondary Communications Port

The I2C Control Block Header holds the primary and secondary port indices.

Generally, there is only 1 connector per DCB display path. TVs are special since one output device could have multiple connectors.

Currently defined values are:

-

0 = 1 Connector

-

1 = 2 Connectors

-

2 = 3 Connectors

-

3 = 4 Connectors

If only one bit of either of the Red, Green or Blue defines in the above DACs field is set, then this field must be set to 1 connector.

If two bits of either of the Red, Green or Blue defines in the above DACs field is set, then this field must be set to 1 or 2 connectors for a S-Video and/or Composite connector. But those connectors cannot be displayed simultaneously.

If three bits of either of the Red, Green or Blue defines in the above DACs field is set, then this field must be set to 2 connectors for both a S-Video and Composite connector.

If the HDTV Bit is set, then we can assume that there will be connectors for YPrPb, S-Video, and Composite off of the Personal Cinema pod. So, this field should be set to 3 connectors.

This field determines the default HDTV Format.

Currently defined values are:

-

0x0 = HDTV 576i

-

0x1 = HDTV 480i

-

0x2 = HDTV 480p @60Hz

-

0x3 = HDTV 576p @50Hz

-

0x4 = HDTV 720p @50Hz

-

0x5 = HDTV 720p @60Hz

-

0x6 = HDTV 1080i @50Hz

-

0x7 = HDTV 1080i @60Hz

-

0x8 = HDTV 1080p @24Hz

-

0x9-0xE = Reserved

-

0xF = Reserved

This field determines the default SDTV Format.

Currently defined values are:

-

0x0 = NTSC_M (US)

-

0x1 = NTSC_J (Japan)

-

0x2 = PAL_M (NTSC Timing w/PAL Encoding - Brazilian Format)

-

0x3 = PAL_BDGHI (US)

-

0x4 = PAL_N (Paraguay and Uruguay Format)

-

0x5 = PAL_NC (Argentina Format)

-

0x6 = Reserved

-

0x7 = Reserved

The TV sub-DACs are labeled 0, 1, 2, and 3 for G80 and later GPUs. There is no plan currently to support external TV encoders. When the CRT is used, sub-DAC 0 is used for Red, sub-DAC 1 is used for Green and sub-DAC 2 is used for Blue, always.

This table should explain how each TVDACs value corresponds to each sub-DAC TV Protocol:

| TVDACs | Composite | S-Video | HDTV | SCART | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

0 |

1 |

2 |

3 |

0 |

1 |

2 |

3 |

0 |

1 |

2 |

3 |

0 |

1 |

2 |

3 |

|

0 |

Invalid |

|||||||||||||||

1 |

Invalid |

|||||||||||||||

2 |

CVBS |

|||||||||||||||

3 |

CVBS |

C |

Y |

|||||||||||||

4 |

CVBS |

|||||||||||||||

5 |

Invalid |

|||||||||||||||

6 |

Invalid |

|||||||||||||||

7 |

CVBS |

C |

Y |

|||||||||||||

8 |

CVBS |

C |

Y |

R/Pr |

G/Y |

B/Pb |

||||||||||

9 |

CVBS |

Y |

C |

R/Pr |

G/Y |

B/Pb |

||||||||||

A |

CVBS |

Y |

C |

G |

B |

R |

CVBS |

|||||||||

B |

CVBS |

C |

Y |

R/Pr |

G/Y |

B/Pb |

||||||||||

C |

CVBS |

Y |

C |

G/Y |

B/Pb |

R/Pr |

G |

B |

R |

CVBS |

||||||

D |

R/Pr |

G/Y |

B/Pb |

|||||||||||||

E |

CVBS |

Y |

C |

R |

G |

B |

CVBS |

|||||||||

F |

CVBS |

Y |

C |

G/Y |

R/Pr |

B/Pb |

R |

G |

B |

CVBS |

||||||

0x10 |

Reserved |

|||||||||||||||

0x11 |

CVBS |

R/Pr |

G/Y |

B/Pb |

||||||||||||

0x12 |

CVBS1 |

CVBS2 |

Y |

C |

G/Y |

B/Pb |

R/Pr |

CVBS |

G |

R |

B |

|||||

0x13 |

Y |

C |

||||||||||||||

Only the entries above in red are currently supported in Core6+.

Here’s how we choose the connector types based on the load:

-

The SCART configuration is chosen if SCART is valid for the board’s TVDACs setting, and loads are detected on all four sub-DACS.

-

The HDTV configuration is chosen if HDTV is valid for the board’s TVDACs setting, SCART was not chosen, and loads are detected on the three sub-DACS that are specified to carry signals for the HDTV configuration.

-

The S-Video configuration is chosen if S-Video is valid for the board’s TVDACs setting, SCART or HTDV were not chosen, and loads are detected on the two sub-DACS that are specified to carry signals for the S-Video configuration.

-

The Composite configuration is chosen if Composite is valid for the board’s TVDACs setting while SCART, HTDV, or S-Video were not chosen.

-

Some configurations allow for two different Composite/CVBS signals. CVBS1 is used if that DAC has a load. Otherwise, we use CVBS2. CVBS1 is the CVBS signal when the 4-pin S-Video to CVBS dongle is used. CVBS2 is the CVBS signal when the 7-pin HDTV component dongle is used (the B/Pb connector on the HDTV component RCA connectors on the 7-pin dongle is labeled as "Comp" for use with CVBS).

-

The S-Video Y signal will always follow the G/Y signal on the 7-pin HDTV component dongle (because the pins match up on the connectors).

-

The S-Video C signal will always follow the R/Pr signal on the 7-pin HDTV component dongle (because the pins match up on the connectors).

-

The CVBS (Composite) signal will always follow the B/Pb signal on the 7-pin HDTV component dongle (because the B/Pb connector is labeled for use as Composite (CVBS)).

-

The CVBS (Composite) signal will always follow the Y signal on the 4-pin S-Video to CVBS dongle (because the dongle has the RCA CVBS signal wired that way).

Communications Control Block

This structure is REQUIRED in the DCB 4.0 spec. It must be listed inside every DCB. The VBIOS and the FCODE will use the data from this structure.

The Communications Control Block provides logical to physical translation of all the different ways that the GPU can use to communicate with other devices on the board or to displays. Prior to DCB 4.0 there were 3 different I2C Ports for GPUs and an extra 2 for Crush (nForce chipset) 11/17. The Northbridge, which holds the integrated GPU, only has 1.5 V signaling, but the DDC/EDID spec requires 3.3 V signaling. So, for Crush, we use two ports on the south bridge to handle the DDC voltage requirements.

|

Note

|

Crush, also known as nForce or nForce2, is a motherboard chipset created by NVIDIA. Crush was released in mid-2001. |

For DCB 4.0, the norm will be 4 I2C ports as exposed on G80. With Display Port added in G98, we’ll expose DPAUX ports as well.

Communications Control Block Header

| Name | Bit width | Values and Meaning |

|---|---|---|

Version |

8 |

Version # of the CCB Header and Entries. CCB 4.0 will start with a value of 0x40 here. A version of 0 here is invalid. |

Header Size |

8 |

Size of the CCB Header in bytes. This is typically 5 bytes. |

Entry Count |

8 |

Number of CCB Entries starting directly after the end of this table. |

Entry Size |

8 |

Size of each entry in bytes. This field should be 4. |

Primary Communication Port |

4 |

Index for the primary communications port. Specifically, if we need to talk with an external device, the port referenced by this index will be the primary port to talk with that device. |

Secondary Communication Port |

4 |

Index for the secondary communications port. Specifically, if we need to talk with an external device, this port referenced by this index will be the secondary port to talk with that device. |

There is one port entry for each port used. A DVI-I connector’s two device entries share the same I2C port.

Communications Control Block Entry

The first upper 8 bits of each entry is called the Access Method. This field indicates how the software should control each port. From NV50 onward a new port mapping was implemented. Older I2C Access methods - CRTC indexed mapping and PCI IO Mapping - have been removed, but their values reserved to allow SW compatibility. Here’s the NV50 and later Defined Access Methods:

| Value | Method |

|---|---|

0 |

Reserved (Prior DCB Usage) |

1 |

Reserved (Prior DCB Usage) |

2 |

Reserved (Prior DCB Usage) |

3 |

Reserved (Prior DCB Usage) |

4 |

Reserved (Prior DCB Usage) |

5 |

I2C Access Method |

6 |

Display Port AUX Channel Access Method |

I2C Access Method

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

I2CAccess = 5 |

Reserved |

Rsv |

DP |

H |

Speed |

Phys Port |

|||||||||||||||||||||||||

| Name | Bit width | Values and Meaning |

|---|---|---|

Physical Port |

4 |

Physical Nv5x Port * 0 = DDC0 * 1 = DDC1 * 2 = DDC2 * 3 = I2C |

Port Speed |

4 |

The I2C spec defines 3 different communication speeds: * Standard - 100 kHz * Fast - 400 kHz * High Speed - 3.4 MHz Each device on an I2C bus must comply with that speed otherwise, the lowest device on that bus will clock stall the speed to what it can handle. High Speed requires extra programming to allow a specific master to send the high speed data. There are programming requirements to also allow for the fallback between higher level speeds and lower levels speeds. No traffic on the I2C port may exceed the speed specified here. Most (perhaps all) DCBs set this field to 0. The currently defined levels are: * 0x0 = Use Defaults (Probably the only one we’ll ever use.) * 0x1 = 100 kHz as per Standard specification * 0x2 = 200 kHz * 0x3 = 400 kHz as per Fast specification * 0x4 = 800 kHz * 0x5 = 1.6 MHz * 0x6 = 3.4 MHz as per High Speed specification * 0x7 = 60 KHz |

Hybrid Pad |

1 |

This bit is used to tell us if we’re enabling Hybrid Pad control for this entry. Hybrid pad control requires that we switch bits in the NV_PMGR_HYBRID_PADCTL area when switching between I2C output and DPAux output. The values here are: * 0 = Normal Mode - Generic I2C Port * 1 = Hybrid Mode - Pad allows for switching between DPAux and I2C |

Physical DP Aux Port |

4 |

This is the physical DP Aux port used only when Hybrid Pad field is in Hybrid Mode. We need this value since NV_PMGR_HYBRID_PADCTL is indexed based on the DP Port value. |

Reserved |

11 |

Set as 0. |

I2C Access Method |

8 |

Must be set to 5 for this Access Method |

Display Port AUX Channel Access Method

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

DP Aux Access = 6 |

Reserved |

Rsvd |

I2C |

H |

Rsvd |

Phys Port |

|||||||||||||||||||||||||

| Name | Bit width | Values and Meaning |

|---|---|---|

Port |

4 |

Physical Display Ports |

H |

1 |

Hybrid Pad |

I2C |

4 |

Physical I2C Port |

Rsvd |

11 |

Reserved. Set as 0. |

Type |

8 |

Display Port AUX Channel Access Method = 6 |

-

0 = AUXCH 0

-

1 = AUXCH 1

-

2 = AUXCH 2

-

3 = AUXCH 3

This bit is used to tell us if we’re enabling Hybrid Pad control for this entry. Hybrid pad control requires that we switch bits in the NV_PMGR_HYBRID_PADCTL area when switching between I2C output and DPAux output. The values here are:

-

0 = Normal Mode - Generic I2C Port

-

1 = Hybrid Mode - Pad allows for switching between DPAux and I2C

This is the physical I2C port used only when Hybrid Pad field is in Hybrid Mode.

Must be set to 6 to indicate Display Port AUX Channel Access Method

Input Devices Table

This structure is optional. It only needs to be defined if the board provides input devices. Also, the VBIOS or FCODE does not need to use this structure. Only the drivers will use it.

The Input Devices are listed at a location in the ROM dictated by the 16-bit Input Devices Pointer listed in the DCB Header. Currently, the maximum number of devices is 8. Each device is listed in one 8-bit entry.

If a device has an Input Device Structure, but not a Personal Cinema Structure defined, we treat that board as a generic VIVO (Video-In, Video-Out) board.

It is assumed that each of these Input Devices is controlled via I2C through the Primary Communications Port.

Input Devices Header

| Name | Bit width | Values and Meaning |

|---|---|---|

Version |

8 |

Version # of the Input Devices Header and Entries. Input Devices 4.0 start with a version of 0x40. |

Header Size |

8 |

Size of the Input Devices Header in Bytes. Initially, this is 4 bytes. |

Entry Count |

8 |

Number of Input Devices Entries starting directly after the end of this table. |

Entry Size |

8 |

Size of Each Entry in bytes. This field should be 1. |

Input Device Entry

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|

VT |

T |

Mode |

|||||

| Name | Bit width | Values and Meaning |

|---|---|---|

Mode |

4 |

This field lists the Mode number that this device supports. If we encounter a Mode of 0xF, that signifies a Skip Entry. This allows for quick removal of a specific entry from the Input Devices. |

Type |

2 |

This field describes the type of input device that is connected. Current defined possible values are: * 0 = VCR, * 1 = TV |

Video Type |

2 |

This field describes the video type of input device that is connected. Currently defined values are: * 0 = CVBS, * 1 = Tuner, * 2 = S-Video |

Personal Cinema Table

|

Note

|

"Personal Cinema" refers to a line of graphics boards with pre-G80 NVIDIA GPUs and on-board television tuners. |

This structure is optional. It only needs to be defined if the board is intending to provide Personal Cinema support. The VBIOS or FCODE does not need to use this structure. Only the drivers will use it.

There are many specific defines needed for the personal cinema in order to know which devices are available. Because there are no entries needed for this table, the normal Entry Count and Entry Size will not be a part of this table for now.

If both the Board ID and the Vendor ID are 0, then the Personal Cinema Table data should be considered invalid. This is akin to other table’s SKIP ENTRY, meaning that we should just skip this table if these IDs are both 0.

If a device has an Input Devices Table, but not a Personal Cinema Structure defined, we treat that board as a generic VIVO (Video-In, Video-Out) board.

It is assumed that each of these Personal Cinema Devices is controlled via I2C through the Primary Communications Port.

Personal Cinema Table Structure

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Vendor ID |

Board ID |

Header Size |

Version |

||||||||||||||||||||||||||||

| 63 | 62 | 61 | 60 | 59 | 58 | 57 | 56 | 55 | 54 | 53 | 52 | 51 | 50 | 49 | 48 | 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

IRCtrl |

PwrCtrlIC |

Demod1 |

ATuner 1 |

SndDcd1 |

Std |

Eio |

|||||||||||||||||||||||||

| 95 | 94 | 93 | 92 | 91 | 90 | 89 | 88 | 87 | 86 | 85 | 84 | 83 | 82 | 81 | 80 | 79 | 78 | 77 | 76 | 75 | 74 | 73 | 72 | 71 | 70 | 69 | 68 | 67 | 66 | 65 | 64 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Demod2 |

R |

T2F |

R |

T1F |

ATuner2 |

Rsvd |

SndDcd2 |

||||||||||||||||||||||||

| Name | Bit width | Values and Meaning |

|---|---|---|

Version |

8 |

Version = 0x40 |

Header Size |

8 |

Size in bytes, 12 for v4.0 |

Board ID |

8 |

Personal Cinema Board ID for this board |

Vendor ID |

8 |

Vendor ID for this board |

Eio |

2 |

Expander IO bus width |

TVStd |

2 |

TV Standard used e.g. NTSC or PAL |

SndDec1 |

4 |

Sound Decoder #1 ID |

ATuner1 |

8 |

Analog Tuner #1 type, the first analog tuner |

Demod1 |

8 |

Demodulator #1, the first digital-signal tuner |

PwrCtrlIC |

4 |

Satellite Dish power controller IC type |

IRCtrl |

4 |

The InfraRed transmitter microcontroller type |

SndDec2 |

4 |

Sound Decoder #2 ID |

Rsvd |

4 |

Reserved, set to 0 |

ATuner2 |

8 |

Analog Tuner #2 type. |

T1F |

3 |

Tuner #1 Functionality, digitial TV, analog TV and FM. |

Reserved |

1 |

Reserved, set to 0 |

T2F |

3 |

Tuner #2 Functionality |

Reserved |

1 |

Reserved, set to 0 |

Demod2 |

8 |

Demodulator #2, the second digital-signal tuner |

Version # of the Personal Cinema Header. The original Personal Cinema table version will start with a value of 0x40 here. If the version is 0 here, then the driver will assume that this table is invalid.

Size of the Personal Cinema Header in bytes. This is 12 bytes for v4.0.

This field lists the Personal Cinema Board ID for this board. This provides a mechanism for SW to differentiate between individual Personal Cinema boards and generic Video-In-Video-Out (VIVO) boards.

Currently defined values are:

-

0x00 = Generic VIVO board or No Personal Cinema Support

-

0x01 = P79

-

0x02 = P104

-

0x03 = P164-NV31

-

0x04 = P164-NV34

-

0x05 = P186-NV35

-

0x06 = P187-NV35

-

0x07 = P178-NV36

-

0x08 = P253-NV43

-

0x09 = P254-NV44

-

0x0A = P178-NV36-A2M

-

0x0B = P293

-

0x0C = P178-NV36-FPGA

-

0x0D = P143-NV34-FPGA

-

0x0E = P143-NV34-Non-FPGA

-

0x10 = P256-NV43

-

0x11 = Compro

-

0x13 = P274-NV41

-

0x21 = Asus AIO

-

0x22 = Asus external tuner

-

0x30 = Customer Reserved 0

-

0x31 = Customer Reserved 1

-

0x32 = Customer Reserved 2

This field lists the Personal Cinema Vendor ID for this board. Current defined possible values are:

-

0x00 = Generic VIVO board or No Personal Cinema Support

-

0xde = NVIDIA

-

0xcb = Compro

-

0x81 = Asus

This field describes the exact number of bits used for the expander IO bus.

Currently defined values are:

-

0 = None or Not Applicable

-

1 = 8 bits

-

2 = 16 bits

-

3 = RF remote

This field describes the TV standard used for the input devices.

Currently defined values are:

-

0 = NTSC

-

1 = PAL/SECAM

-

2 = Worldwide

-

3 = Reserved

This field describes the first Sound Decoder used on the board. Current defined possible values are:

-

0 = Mono

-

2 = A2 (TDA9873)

-

3 = NICAM (TDA9874)

-

4 = BTSC (TDA9850)

-

5 = FM-FM Japan (TA8874z)

-

6 = BTSC/EIAJ (SAA7133/SAA7173)

-

7 = A2,NICAM (SAA7134/SAA7174)

-

8 = Worldwide (SAA7135/SAA7175)

-

9 = Micronas MSP 3425G (NTSC)

-

10 = Micronas MSP 3415G (PAL)

-

11 = SAA7174A

-

12 = SAA7171

-

15 = Not Present

This field describes the first analog-signal tuner used on the board.

Currently defined values are:

-

0x00 = Not Present

-

0x01 = Philips FI1216 MK2

-

0x02 = Philips FI1216 MF

-

0x03 = Philips FI1236 MK2

-

0x04 = Philips FI1246 MK2

-

0x05 = Philips FI1256 MK2

-

0x06 = Philips FQ1216 ME

-

0x07 = Philips FQ1216 ME MK3

-

0x08 = Philips FQ1236 ME MK3

-

0x09 = Philips TDA 8275

-

0x11 = Temic 4036FY5,4032FY5

-

0x12 = Temic 4006FH5,4002FH5

-

0x13 = Temic 4066FY5,4036FY5

-

0x14 = Temic 4016FY5,4012FY5

-

0x15 = Temic 4136

-

0x16 = Temic 4146

-

0x17 = Microtune MT2040

-

0x18 = Microtune MT2050

-

0x19 = Microtune 7102DT5

-

0x20 = Microtune 7132DT5

-

0x21 = Microtune MT2060

-

0x22 = Microtune 4039FR5

-

0x23 = Microtune 4049FM5

-

0x30 = LG TALN-M200T (PAL)

-

0x31 = LG TALN-H200T (NTSC)

-

0x32 = TALN-S200T (SECAM L/L' & PAL B/G, I/I, D/K)

-

0x60 = Samsung TEBN9282PK01A

-

0x81 = Philips FM1216

-

0x82 = Philips FM1216MF

-

0x83 = Philips FM1236

-

0x84 = Philips FM1246

-

0x85 = Philips FM1256

-

0x86 = Philips FM1216 ME

-

0x87 = Philips FM1216 ME MK3

-

0x88 = Philips FM1236 ME MK3

The first digital-signal tuner used this board. This field has these hex defines:

-

0x00 = Not present

-

0x01 = TDA9885 (PAL/NTSC Analog)

-

0x02 = TDA9886 (PAL/NTSC/SECAM Analog)

-

0x03 = TDA9887 (PAL/NTSC/SECAM QSS Analog)

-

0x04 = Philips SAA7171

-

0x10 = Conexant CX24121

-

0x15 = Phillips TDA8260TW

-

0x16 = Zarlink MT352

-

0x17 = LGDT3302

-

0x18 = Micronas DRX3960A

Satellite Dish power controller. This field has these hex defines:

-

0 = Not present

-

1 = LNBP21 - I2C Address 0x10

The microcontroller chip used for infrared (IR) transmitting to control other IR devices. This field has these values

-

0 = Not present

-

6 = PIC12F629

-

7 = PIC12CE673

This field describes a possible second Sound Decoder used on the board. The values are the same as with Sound Decoder #1.

This field describes a possible second analog-signal tuner used on the board. The values are the same as with Tuner Type #1.

This field describes the functionality supported by Tuner #1.

Currently defined values are:

-

0 = None

-

1 = Digital TV

-

2 = Analog TV

-

3 = Analog + Digital TV

-

4 = FM

-

5 = Digital + FM

-

6 = Analog + FM

-

7 = Analog + Digital + FM

This field describes the functionality allowed by Tuner Type #2 field. The currently defined values are the same as those for Tuner #1 Functionality.

The possible second digital-signal tuner used this board. This field has the same defines as Demodulator #1.

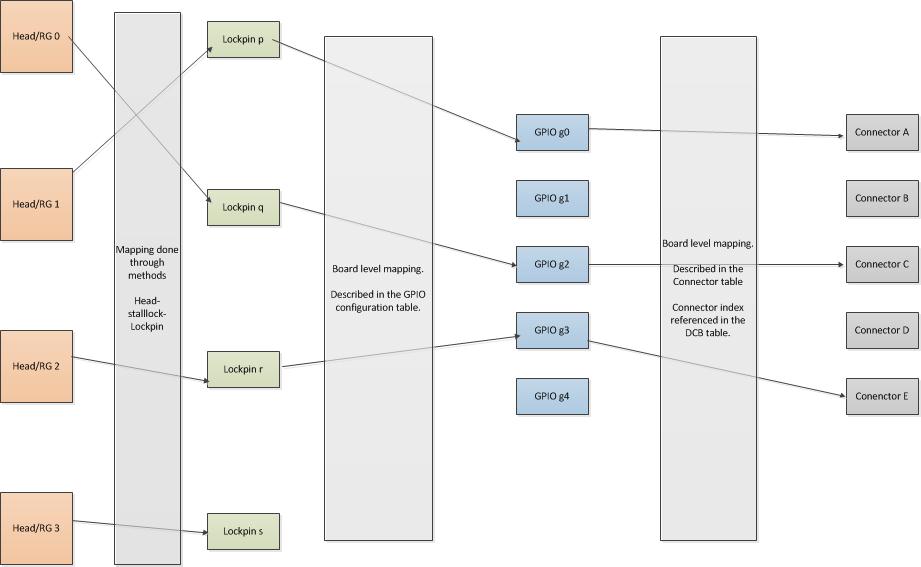

GPIO Assignment Table

The GPIO Assignment table creates a logical mapping of function-based usage names to physical GPIOs within the GPU. Each pin has

-

a logical ON State and

-

a logical OFF State.

Each state can be distinctly defined physically via:

-

Sending output high to the GPIO,

-

Sending output low to the GPIO, or

-

Tristating the GPIO (Setting it to Input Mode).

Alternately, specific GPIOs can also be assigned to carry Pulse Width Modulated (PWM) signals. This can be used for fan speed control or backlight power control.

This table is required in all ROMs. It must be listed inside every DCB. The VBIOS and the FCODE will use the data from this structure.

GPIO Assignment Table Header

When moving to GF110, the HW team merged the Normal/Alternate/Sequencer modes of the GPIO into one 8 bit field in a GPIO register. In order to better manage that change, we decided to increase the revision from the initial 0x40 version to 0x41 and re-organize the bit fields in each GPIO table entry to accommodate a new field that matches the field in the HW register directly.

Version 0x41, as used for GF11x+ / Core75 and future cores, is listed below.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Entry Size = 5 |

Entry Count |

Header Size = 6 |

Version = 0x41 |

||||||||||||||||||||||||||||

| 47 | 46 | 45 | 44 | 43 | 42 | 41 | 40 | 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

GPIOAssTabPtr |

|||||||||||||||

Version # of the GPIO Assignment Table Header and Entries. The current GPIO Assignment Table version is 4.1 or a value of 0x41 in this field. If this version is 0, then the driver will assume that this table is invalid.

Size of the GPIO Assignment Table in bytes. For version 4.1 this is 6 bytes.

Number of GPIO Assignment Table Entries starting directly after the end of this header.

Size of Each Entry in bytes. For version 4.0, this was 4 bytes. For version 4.1, this is now 5 bytes.

Pointer to the External GPIO Assignment Master Table. This field can be set to 0 to indicate no support for this table.

GPIO Assignment Table Entry

Please note that this structure below is for version 4.1.

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

PM |

R |

GS |

Input HW Select |

Output HW Select |

Function |

I |

IO |

PinNum |

|||||||||||||||||||||||

| 39 | 38 | 37 | 36 | 35 | 34 | 33 | 32 |

|---|---|---|---|---|---|---|---|

OE |

OT |

FE |

FT |

LockPin |

|||

| Name | Bit width | Values and Meaning |

|---|---|---|

PinNum |

6 (5:0) |

GPIO Pin Number |

IO |

1 (6:6) |

I/O Type |

I |

1 (7:7) |

Initialize pin state |

Function |

8 (15:8) |

|

Output HW select |

8 (23:16) |

Output hardware function setting |

Input HW select |

5 (28:24) |

Input hardware function setting |

GS |

1 (29:29) |

GSYNC Header |

R |

1 (30:30) |

Reserved |

PM |

1 (31:31) |

Pulse Width Modulate |

LockPin |

4 (35:32) |

Lock Pin Number |

FT |

1 (36:36) |

Off Data |

FE |

1 (37:37) |

Off Enable |

OT |

1 (38:38) |

On Data |

OE |

1 (39:39) |

On Enable |

The GPIO number associated with this entry. Older chips have a maximum of 9 GPIO pins. G80+ have 15 GPIOs in register space. This field must be 0 if the I/O Type field is set to NV_GPIO_IO_TYPE_DEDICATED_LOCK_PIN.

The I/O Type field is used to specify if this entry represents an actual GPIO or instead represents a similar type of entity. This field is an enumeration that currently has the following values:

-

0 = NV_GPIO_IO_TYPE_GPIO - This entry represents a normal internal GPIO.

-

1 = NV_GPIO_IO_TYPE_DEDICATED_LOCK_PIN - This entry represents an internal dedicated lock pin. No actual GPIO is associated with the lock pin. The GPIO Number field must be set to zero.

This field specifies the initial state to set the GPIO to during boot. If this bit is 0, then the software will initialize the GPIO at boot to the settings specified by "Off Data" and "Off Enable". If this bit is 1, then the software will initialize the GPIO at boot to the settings specified by "On Data" and "On Enable".

This lists the function of each GPIO pin. Here’s a list of the function numbers and a short description of each:

-

0 = LCD0 backlight: Backlight control. LCD0 corresponds to the LCD0 defined in the LCD ID field in the Connector Table.

-

1 = LCD0 power: Panel Power control. LCD0 corresponds to the LCD0 defined in the LCD ID field in the Connector Table.

-

2 = LCD0 Power Status: Panel Power status. LCD0 corresponds to the LCD0 defined in the LCD ID field in the Connector Table.

-

3 = VSYNC: Alternate VSync signal using GPIO pin.

-

4 = VSEL0: Voltage Select Bit 0

-

5 = VSEL1: Voltage Select Bit 1

-

6 = VSEL2: Voltage Select Bit 2

-

7 = Hotplug A: 1st Hotplug signal

-

8 = Hotplug B: 2nd Hotplug signal

-

9 = Fan: Fan control. Can be on or off, or pulse width modulation to control speed.

-

10 = Reserved

-

11 = Reserved

-

12 = DAC 1 Select: DAC 1 mux select that allows us to switch between using the CRT (Off state) or TV (On State) filters on the board.

-

13 = DAC 1 Alternate Load Detect: When the DAC 1 is not currently switched to a device that needs detection, this GPIO pin can be used to detect the alternate load on the green channel.

-

14 = Stereo DAC Select: Chooses which DAC to use for the stereo goggles.

-

15 = Stereo toggle: Switch between Left and Right eyes for the stereo goggles.

-

16 = Thermal and External Power Detect: Sense bit when there’s a thermal event or the external power connector is connected or removed from the board.

-

17 = Thermal Event Detect: Sense bit when there’s a thermal event sent from the thermal device.

-

18 = Vtg rst: Input Signal from daughter card for Frame Lock interface headers.

-

19 = Sus stat: Input requesting the suspend state be entered

-

20 = Spread0: Bit 0 of output to control Spread Spectrum if the chip isn’t I2C controlled.

-

21 = Spread1: Bit 1 of output to control Spread Spectrum if the chip isn’t I2C controlled.

-

22 = VDS FrameID0 - Bit 0 of the frame ID when using Virtual Display Switching.

-

23 = VDS FrameID1: Bit 1 of the frame ID when using Virtual Display Switching.

-

24 = FBVDDQ Select: Selects between:

-

: ON state: High FBVDD/Q voltage (i.e. 1.8V)

-

: OFF State: Low FBVDD/Q voltage (i.e. 1.5V)

-

25 = Customer: This function is here to be used by the OEM. It just reserves the GPIO so our software will know not to use it.

-

26 = VSEL 3: Voltage Select Bit 3

-

27 = VSEL Default - Allow switching from default voltage (1) to selected voltage (0).

-

28 = Tuner

-

29 = Current Share

-

30 = Current Share Enable

-

31 = LCD0 Self Test. LCD0 corresponds to the LCD0 defined in LCD ID field in Connector Table.

-

32 = LCD0 Lamp Status. LCD0 corresponds to the LCD0 defined in LCD ID field in Connector Table.

-

33 = LCD0 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD0 corresponds to the LCD0 defined in LCD ID field in Connector Table.

-

34 = Required Power Sense. Similar to 16, but without the thermal half.

-

35 = OverTemp - This GPIO will assert when the GPU has reached some adjustable temperature threshold

-

36 = HDTV Select: Allows selection of lines driven between SDTV - Off state, and HDTV - On State.

-

37 = HDTV Alt-Detect: Allows detection of the connectors that are not selected by HDTV Select. That is, if HDTV Select is currently selecting SDTV, then this GPIO would allow us to detect the presence of the HDTV connection.

-

38 = Reserved

-

39 = Optional Power Sense. Similar to 16 and 34, but without the thermal half and not necessary for normal non-overclocked operation.1

-

40 = DAC 0 Select: DAC 0 mux that allows us to switch between using the CRT (Off state) or TV (On State) filters on the board.

-

41 = Framelock daughter-card interrupt

-

42 = SW Performance Level Slowdown. When asserted, the SW will lower it’s performance level to the lowest state.

-

43 = HW Slowdown Enable. On assertion HW will slowdown clocks (NVCLK, HOTCLK) using either _EXT_POWER, _EXT_ALERT or _EXT_OVERT settings (depends on GPIO configured: 12, 9 & 8 respectively). Than SW will take over, limit GPU p-state to battery level and disable slowdown. On deassertion SW will reenable slowdown and remove p-state limit. System will continue running full clocks.

-

44 = Disable Power Sense. If asserted, this GPIO will remove the power sense circuit from affecting HW Slowdown.

-

45 = RSET HDTV Select. Allows selecting between SDTV, On State, and HDTV, Off State, RSET values during TV detection.

-

46 = FBVREF Select: Selects between:

-

ON state: High FBVREF voltage (i.e. 70% FBVDDQ)

-

OFF state: Low FBVREF voltage (i.e. 50% FBVDDQ)

-

-

47 = Reserved

-

48 = Generic Initialized: This GPIO is used, but does not have a specific function assigned to it or has a function defined elsewhere. System software should initialize this GPIO using the _INIT values for the chip. This function should be specified when a GPIO needs to be set statically during initialization. This is different than function 25, which implies that the GPIO is not used by NVIDIA software.

-

49 = Inquiry for HD over SD TV boot preference. Allows user to select whether to boot to SDTV or component output by default.

-

50 = Digital Encoder Interrupt Enable: For Si1930uC, a GPIO will be set ON to trigger interrupt to Si1930uC to enable I2C communication. When I2C transactions to the Si1930uC are complete, the drivers will set this GPIO to OFF.

-

51 = Selects I2C communications between either DDC or I2C

-

52 = Thermal Alert: Interrupt input from external thermal device. Indicates that the device needs to be serviced.

-

53 = Thermal Critical: Comparator-driven input from external thermal device. Indicates that a temperature is above a critical limit.

-

54 = Reserved

-

55 = Reserved

-

56 = Reserved

-

57 = Reserved

-

58 = Reserved

-

59 = Reserved

-

60 = SCART Select: Allows selection of lines driven between SDTV (S-Video, Composite) and SDTV (SCART).

-

61 = Fan Speed Sense. This GPIO will sense a fan’s tachometer output (on 4-wire fans). In the beginning, it will be more for sensing a stuck fan than determining speed. Later GPUs will be able to measure the fan’s speed internally from the GPIO.

-

62 = Reserved

-

63 = ExtSync0 - Used with external framelock with GSYNC products. It also could be used for raster lock.

-

64 = SLI Raster Sync A: This signal is carried across the SLI bus to synchronize the RG between GPUs. This signal will always be set as Alternate.

-

65 = SLI Raster Sync B: This signal is carried across the SLI bus to synchronize the RG between GPUs. This signal will always be set as Alternate. This signal is just the second GPIO that can be used for Raster sync from each GPU. It should only be defined when we have 2 pin sets being used on one board to allow more than two GPUs to run in SLI mode. One will be used with one pin set for input and the other will be used with the other pin set for output.

-

66 = Swap Ready In A: This signal, which is related to Fliplocking, is used to sense the state of the FET drain, which is pulled high and is connected to the Swap Ready pin on the Distributed Rendering connector.

-

67 = Swap Ready Out: This signal, which is related to Fliplocking, is used to drive the gate of an external FET.

-

68 = Available

-

69 = SCART 0: Bit 0 of the SCART Aspect Ratio Field

-

70 = SCART 1: Bit 1 of the SCART Aspect Ratio Field

-

GPIOs 69 and 70 define a 2 bit SCART Aspect Ratio Field. Here’s the possible values for the SCART Aspect Ratio Field:

-

0 = 4:3(12V)

-

1 = 16:9(6V)

-

2 = Undefined

-

3 = SCART inactive (0 V)

-

-

71 HD Dongle Strap 0: Bit 0 of the HD Dongle Strap Field

-

72 HD Dongle Strap 1: Bit 1 of the HD Dongle Strap Field

|

Note

|

GPIOs 71 and 72 define a 2 bit HD Dongle Strap Field. These two bits index into an array found at the HDTV Translation Table that will determine the default HD standard. |

-

73 = Thermal Alert Output: Output signal that indicates to other board component(s) that the gpu’s internal temp has exceeded a certain threshold for a duration longer than a programmed interval.

-

74 = DisplayPort to DVI dongle present A, when this GPIO asserts, we need to configure DisplayPort encoder to output TMDS signal.

-

75 = DisplayPort to DVI dongle present B, when this GPIO asserts, we need to configure DisplayPort encoder to output TMDS signal.

-

76 = Power Alert, when this GPIO asserts, the on-board power supply controller needs attention.

-

77 = DAC 0 Load Detect: When the DAC 0 is not currently switched to a device that needs detection, this GPIO pin can be used to detect the alternate display’s load on the green channel.

-

78 = Analogix Encoder External Reset: For Analogix encoder, a GPIO is used to control the RESET# line.

-

79 = I2C SCL Keeper Circuit Enable. See {{Bug|273429}}. Possible logical values are:

-

OFF state: Normal operation (do nothing)

-

ON state: Enable the hardware to detect slave-issued stretches on the SCL line and hold SCL low.

-

-

80 = DVI to DAC connector switch. This GPIO allows for DAC 0 (TV) to be selected to route to the DVI Connector when the GPIO is set to the logical OFF state. When the GPIO is set to logical ON state, DAC 1 (CRT) will be routed to the DVI connector.

-

81 = Hotplug C: 3rd Hotplug signal

-

82 = Hotplug D: 4th Hotplug signal

-

83 = DisplayPort to DVI dongle present C, when this GPIO asserts, we need to configure DisplayPort encoder to output TMDS signal.

-

84 = DisplayPort to DVI dongle present D, when this GPIO asserts, we need to configure DisplayPort encoder to output TMDS signal.

-

85 = Maxim Max6305 or compatible external reset controller. Enabled is Active Low so init value should be Active High [No inversions]

-

86 = Active display LED to indicate the GPU with active display in SLI mode.

-

87 = SPDIF input.

-

88 = TOSLINK input.

-

89 = SPDIF/TOSLINK Select. When GPIO is set LOW, SPDIF is selected. When GPIO is set HI, TOSLINK is selected.

-

90 = DPAUX/I2C select A. When this GPIO is set to Logical ON state, DPAUX will be selected. Logical OFF state selects I2C.

-

91 = DPAUX/I2C select B. When this GPIO is set to Logical ON state, DPAUX will be selected. Logical OFF state selects I2C.

-

92 = DPAUX/I2C select C. When this GPIO is set to Logical ON state, DPAUX will be selected. Logical OFF state selects I2C.

-

93 = DPAUX/I2C select D. When this GPIO is set to Logical ON state, DPAUX will be selected. Logical OFF state selects I2C.

-

94 = Hotplug E: 5th Hotplug signal

-

95 = Hotplug F: 6th Hotplug signal

-

96 = Hotplug G: 7th Hotplug signal

-

99 = GPIO External Device 1 Interrupt - Used to surface an interrupt from a GPIO external device

-

106 = Switched Outputs: This GPIO is used by the switched outputs table. A switched outputs GPIO must be processed by the INIT_GPIO_ALL devinit opcode and set to its init state.

-

107 = Customer Asyncronous Read/Write - Allows a customer to use the GPIO for whatever purpose they want.

-

108 = Access to MXM 3.0 bus’s Direct GPIO0 (Pin 26). Once the system has the MXM structure/GPIO Device structure which defines usage of Direct GPIO0, this GPU’s GPIO is the physical pin to take on any enabling/detection/disabling function defined in the MXM Output Device data structure with MXM Direct GPIO0.

-

109 = Access to MXM 3.0 bus’s Direct GPIO1 (Pin 28). Once the system has the MXM structure/GPIO Device structure which defines usage of Direct GPIO1, this GPU’s GPIO is the physical pin to take on any enabling/detection/disabling function defined in the MXM Output Device data structure with MXM Direct GPIO1.

-

110 = Access to MXM 3.0 bus’s Direct GPIO2 (Pin 30). Once the system has the MXM structure/GPIO Device structure which defines usage of Direct GPIO2, this GPU’s GPIO is the physical pin to take on any enabling/detection/disabling function defined in the MXM Output Device data structure with MXM Direct GPIO2.

-

111 = HW Only Slowdown Enable. On assertion HW will slowdown clocks (NVCLK, HOTCLK) using _EXT_POWER settings (use only with GPIO12). No software action will be taken. On deassertion HW will release clock slowdown.

-

112 = Swap Ready In B: This signal, which is related to Fliplocking, is used to sense the state of the FET drain, which is pulled high and is connected to the Swap Ready pin on the Distributed Rendering connector.

-

113 = Trigger condition for PMU: Can either be triggered by system notify bit set in SBIOS postbox command register or an error entering into deep-idle.

-

114 = Reserved for Swap Ready Out B

-

115 = VSEL4: Voltage Select Bit 4

-

116 = VSEL5: Voltage Select Bit 5

-

117 = VSEL6: Voltage Select Bit 6

-

118 = VSEL7: Voltage Select Bit 7

-

119 = LVDS Fast switch mux

-

120 = Fan Failsafe PWM: The functionality controls FAN fail safe PWM generator. If function is present in VBIOS, GPIO should be configured as normal output and initially asserted. Once RM is loaded and FAN control is successfully initialized RM will dessert this pin to allow FAN_PWM control.

-

121 = External Power Emergency: This GPIO provides an input to let SW know when the GPU does not have enough power to initialize.

-

122 = NVVDD PSI: The NVVDD Power State Indicator (PSI) signals the NVVDD power supply controller to switch to reduced phase operation (typically 1 or 2 phases) for efficiency in low power states. Here are the logical states:

-

ON state: Enable low power state (reduced phase operation)

-

OFF state: Disable low power state (all phase operation)

-

-

123 = Fan with Overtemp: denotes that the pin will be driven from PWM source that has capability to MAX duty cycle based on the thermal ALERT signal, as opposed to the already present "Fan" function which only outputs PWM. This PWM source is independent from the pwm source for "Fan" function.

-

124 = POSTed GPU LED to indicate the GPU that was POSTed by the SBIOS.

-

125 = Reserved

-

126 = Reserved

-

127 = Reserved

-

128 = SMPBI Event Notification: Notifies the EC (or client of the SMBus Post Box Interface) of a pending GPU event requiring its attention.

-

129 = PWM based serial VID voltage control.

-

130 = Reserved

-

131 = SLI Bridge LED Brightness - Allow SLI Bridge brightness adjustment via PWM. (Must have PWM set when this is selected.)

-

132 = Cover LOGO LED Brightness - Allow Cover LOGO brightness adjustment via PWM. (Must have PWM set when this is selected.)

-

133 = Panel Self Refresh Frame Lock A : This function is defined for Self-Refresh Panel. The SR panel will send the frame-lock interrupt to GPU to sync the raster frame signal.

-

134 = FB Clamp: This function is used to monitor the FB clamp signal driven by the Embedded Controller (EC) for JT memory self-refresh entry and exit.

-

135 = FB Clamp Toggle Request: This function is used to request the Embedded Controller (EC) to toggle the FB clamp signal.

-

136 = Reserved

-

137 = Reserved

-

138 = LCD1 backlight: Backlight control. LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

139 = LCD1 power: Panel Power control. LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

140 = LCD1 Power Status: Panel Power status. LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

141 = LCD1 Self Test. LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

142 = LCD1 Lamp Status. LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

143 = LCD1 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD1 corresponds to the LCD1 defined in LCD ID field in Connector Table.

-

144 = LCD2 backlight: Backlight control. LCD2 corresponds to the LCD2 defined in LCD ID field in Connector Table.

-

145 = LCD2 power: Panel Power control. LCD2 corresponds to the LCD2 defined in LCD ID field in Connector Table.

-

146 = LCD2 Power Status: Panel Power status. LCD2 corresponds to the LCD2 defined in LCD ID field in Connector Table.

-

147 = LCD2 Self Test. LCD2 corresponds to the LCD2 defined in LCD ID field in

-

Connector Table.

-

148 = LCD2 Lamp Status. LCD2 corresponds to the LCD2 defined in LCD ID field in Connector Table.

-

149 = LCD2 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD2 corresponds to the LCD2 defined in LCD ID field in Connector Table.

-

150 = LCD3 backlight: Backlight control. LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

151 = LCD3 power: Panel Power control. LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

152 = LCD3 Power Status: Panel Power status. LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

153 = LCD3 Self Test. LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

154 = LCD3 Lamp Status. LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

155 = LCD3 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD3 corresponds to the LCD3 defined in LCD ID field in Connector Table.

-

156 = LCD4 backlight: Backlight control. LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

157 = LCD4 power: Panel Power control. LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

158 = LCD4 Power Status: Panel Power status. LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

159 = LCD4 Self Test. LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

160 = LCD4 Lamp Status. LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

161 = LCD4 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD4 corresponds to the LCD4 defined in LCD ID field in Connector Table.

-

162 = LCD5 backlight: Backlight control. LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

163 = LCD5 power: Panel Power control. LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

164 = LCD5 Power Status: Panel Power status. LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

165 = LCD5 Self Test. LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

166 = LCD5 Lamp Status. LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

167 = LCD5 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD5 corresponds to the LCD5 defined in LCD ID field in Connector Table.

-

168 = LCD6 backlight: Backlight control. LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

169 = LCD6 power: Panel Power control. LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

170 = LCD6 Power Status: Panel Power status. LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

171 = LCD6 Self Test. LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

172 = LCD6 Lamp Status. LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

173 = LCD6 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD6 corresponds to the LCD6 defined in LCD ID field in Connector Table.

-

174 = LCD7 backlight: Backlight control. LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

175 = LCD7 power: Panel Power control. LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

176 = LCD7 Power Status: Panel Power status. LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

177 = LCD7 Self Test. LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

178 = LCD7 Lamp Status. LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

179 = LCD7 Brightness - Allow brightness adjustment via PWM. (Must have PWM set when this is selected.). LCD7 corresponds to the LCD7 defined in LCD ID field in Connector Table.

-

180 = Reserved

-

255 = 0xFF = Skip Entry. This allows for quick removal of an entry from the GPIO Assignment table.

This field specifies HW Select value which has to be directly written by software into the OUTPUT register field for deciding which output HW function/enumerant will drive the PIN.

Values as specified in class20x HW manual

-

0x00 = SEL_NORMAL

-

0x40 = SEL_RASTER_SYNC_0

-

0x41 = SEL_RASTER_SYNC_1

-

0x42 = SEL_RASTER_SYNC_2

-

0x43 = SEL_RASTER_SYNC_3

-

0x48 = SEL_STEREO_0

-

0x49 = SEL_STEREO_1

-

0x4A = SEL_STEREO_2

-

0x4B = SEL_STEREO_3

-

0x50 = SEL_SWAP_READY_OUT_0

-

0x51 = SEL_SWAP_READY_OUT_1

-

0x52 = SEL_SWAP_READY_OUT_2

-

0x53 = SEL_SWAP_READY_OUT_3

-

0x58 = SEL_THERMAL_OVERT

-

0x59 = SEL_FAN_ALERT

-

0x5A = SEL_THERMAL_LOAD_STEP_0

-

0x5B = SEL_THERMAL_LOAD_STEP_1

-

0x5C = SEL_PWM_OUTPUT

-

0x80 = SEL_SOR0_TMDS_OUT_PWM

-

0x81 = SEL_SOR0_TMDS_OUT_PINA

-

0x82 = SEL_SOR0_TMDS_OUT_PINB

-

0x84 = SEL_SOR1_TMDS_OUT_PWM

-

0x85 = SEL_SOR1_TMDS_OUT_PINA

-

0x86 = SEL_SOR1_TMDS_OUT_PINB

-

0x88 = SEL_SOR2_TMDS_OUT_PWM

-

0x89 = SEL_SOR2_TMDS_OUT_PINA

-

0x8A = SEL_SOR2_TMDS_OUT_PINB

-

0x8C = SEL_SOR3_TMDS_OUT_PWM

-

0x8D = SEL_SOR3_TMDS_OUT_PINA

-

0x8E = SEL_SOR3_TMDS_OUT_PINB

This field specifies the input HW function number which needs to be routed to the given pin (given by GPIO Number) which is also equivalent to the index of the INPUT_CNTL register that needs to be programmed.

Right now the manual specifies space for 24 functions(1-24) which are given below. Note that 0 is not a valid input function in HW and is used only to specify that no input function needs to be programmed on the given pin.

-

00 / 0x00 = No Input function needs to be programmed on the given pin. Note that 0 is not a valid input value in HW.

-

01 / 0x01 = NV_PMGR_GPIO_INPUT_FUNC_AUX_HPD(0)

-

02 / 0x02 = NV_PMGR_GPIO_INPUT_FUNC_AUX_HPD(1)

-

03 / 0x03 = NV_PMGR_GPIO_INPUT_FUNC_AUX_HPD(2)

-

04 / 0x04 = NV_PMGR_GPIO_INPUT_FUNC_AUX_HPD(3)

-

09 / 0x09 = NV_PMGR_GPIO_INPUT_FUNC_RASTER_SYNC(0)

-

10 / 0x0A = NV_PMGR_GPIO_INPUT_FUNC_RASTER_SYNC(1)

-

11 / 0x0B = NV_PMGR_GPIO_INPUT_FUNC_RASTER_SYNC(2)

-

12 / 0x0C = NV_PMGR_GPIO_INPUT_FUNC_RASTER_SYNC(3)

-

17 / 0x11 = NV_PMGR_GPIO_INPUT_FUNC_SWAP_READY(0)

-

18 / 0x12 = NV_PMGR_GPIO_INPUT_FUNC_SWAP_READY(1)

-

21 / 0x15 = NV_PMGR_GPIO_INPUT_FUNC_THERMAL_OVERTEMP

-

22 / 0x16 = NV_PMGR_GPIO_INPUT_FUNC_THERMAL_ALERT

-

23 / 0x17 = NV_PMGR_GPIO_INPUT_FUNC_POWER_ALERT

-

24 / 0x18 = NV_PMGR_GPIO_INPUT_FUNC_TACH

GSYNC Header Connection. Possible values are:

-

0 - Not Connected

-

1 - Connected

RM is responsible for discerning Raster Sync or Flip Lock from the GPIO Function.

If this bit is 1, then this GPIO is used with PWM.

The lock pin number associated with this entry. In ISO designs there are currently four lock pins that are either assigned to GPIO pins or internal dedicated pins. This only applies to a subset of GPIO functions. Depending on the chip, some lock pins are done with real GPIO’s so they have a real GPIO number and the I/O Type Field is set to NV_GPIO_IO_TYPE_GPIO, while other lock pins do not have a real GPIO so they are set to NV_GPIO_IO_TYPE_DEDICATED_LOCK_PIN and the GPIO number is meaningless (but is always set to zero). This field must be 0xF for GPIO functions that do not involve a lock pin.

This field determines in what physcial data output must be present on the GPIO pin to indicate the logical OFF signal. If this bit is 0, then the software will set the GPIO pin to 0 when it wants to turn the function off.

This field determines in which physical direction the GPIO should be placed when requesting the logical function to be OFF. If this bit is 0, then the GPIO will be set as an Output when OFF is requested. If this bit is a 1, then the GPIO will be set as an Input when OFF is requested.

This field determines what physical data output must be present on the GPIO pin to indicate the logical ON signal. If this bit is 0, then the software will set the GPIO pin to 0 when it wants to turn the function on.